что такое архитектура эвм в информатике

Архитектура ЭВМ (часть 1)

Данный материал подготовлен в мою преподскую бытность, как лекция для студентов по дисциплине «Компьютерная схематехника». Может кому он будет интересен

Традиционная архитектура ЭВМ,

Основные устройства, их характеристики и назначения. Архитектура типа «общая шина».

Форматы данных и команд. Особенности адресации памяти

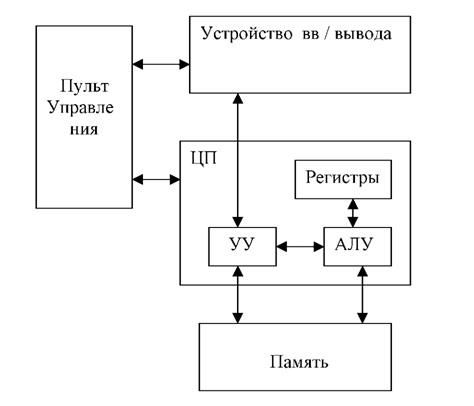

Любой IBM PC совместимый компьютер построен по принципу описанному ещё Джорджем фон Нейманом в 1945м году, его основные составляющие – блок управления, арифметико-логическое устройство, память и устройство ввода-вывода. В компьютере реализован принцип хранимой программы, т.е. данные и программа хранятся в одной и той же памяти. ЦП выбирает и исполняет команды из памяти последовательно, адрес следующей команды задаётся счётчиком адреса, такой принцип называется последовательной передачей управления. Подобная архитектура является не единственно приемлемой, есть ещё потоковые компьютеры и разрабатываются новые типы вычислительных машин.

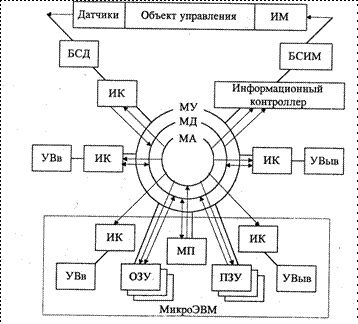

На рис. 1 приведена схема логической структуры микро¬процессорной системы. МикроЭВМ — это совокупность микропроцессора (МП), ОЗУ и ПЗУ вместе с устройствами ввода-вывода (УВВ), предназначенными для работы с оператором или с другой электронной системой. В МП систему входит также аппаратурный блок — информационный контроллер ИК, приводящий все связи и сигналы УВВ разных типов к стан¬дартному виду. ИК имеет стандартный интерфейс со стороны подключения к информационной магистрали, состоящей из ма¬гистралей адресов, данных и управления (МА, МД, МУ), и нестандартный интерфейс со стороны УВВ.

МикроЭВМ становится центральной частью электронной системы контроля и управления, когда она вводится в контур управления некоторого объекта (процесса) ОУ. Для сопряжения с микроЭВМ ОУ оснащается датчиками состояния (Д) и исполнительными механизмами (ИМ). Для согласования интерфейсов Д и ИМ подключаются через блоки сопряжения (БС).

Рассмотренная структура отражает магистрально-модульный принцип организации МПС. Отдельные блоки являются функци¬онально законченными модулями со своими встроенными схемами управления, выполненными в виде одного или нескольких кристаллов БИС, заключенных в корпуса с соответствующим числом выводов. Межмодульные связи и обмен информацией меж¬ду модулями осуществляются посредством магистралей — коллективных шин.

Структура ВМ классической фон Неймановской архитектуры

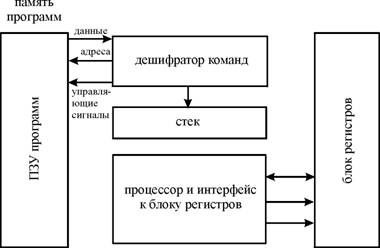

Структура Гарвардской архитектуры

В качестве недостатка архитектуры фон Неймана можно назвать возможность непреднамеренного нарушения работоспособности системы (программные ошибки) и преднамеренное уничтожение ее работы (вирусные атаки). В Гарвардской архитектуре принципиально различаются два вида памяти микропроцессора:

• Память программ (для хранения инструкций микропроцессора)

• Память данных (для временного хранения и обработки переменных)

В гарвардской архитектуре принципиально невозможно осуществить операцию записи в память программ, что исключает возможность случайного разрушения управляющей программы в случае ошибки программы при работе с данными или атаки третьих лиц. Кроме того, для работы с памятью программ и с памятью данных организуются отдельные шины обмена данными (системные шины), как это показано на рисунке 3.

Эти особенности определили области применения гарвардской архитектуры. Гарвардская архитектура применяется в микроконтролерах и в сигнальных процессорах, где требуется обеспечить высокую надёжность работы аппаратуры. В сигнальных процессорах Гарвардская архитектура дополняется применением трехшинного операционного блока микропроцессора. Трехшинная архитектура операционного блока позволяет совместить операции считывания двух операндов с записью результата выполнения команды в оперативную память микропроцессора. Это значительно увеличивает производительность сигнального микропроцессора без увеличения его тактовой частоты.

В Гарвардской архитектуре характеристики устройств памяти программ и памяти данных не всегда выполняются одинаковыми. В памяти данных и команд могут различаться разрядность шины данных и распределение адресов памяти. Часто адресные пространства памяти программ и памяти данных выполняют различными. Это приводит к различию разрядности шины адреса для этих видов памяти. В микроконтроллерах память программ обычно реализуется в виде постоянного запоминающего устройства, а память данных — в виде ОЗУ. В сигнальных процессорах память программ вынуждены выполнять в виде ОЗУ. Это связано с более высоким быстродействием оперативного запоминающего устройства, однако при этом в процессе работы осуществляется защита от записи в эту область памяти.

Применение двух системных шин для обращения к памяти программ и памяти данных в гарвадской архитектуре имеет два недостатка — высокую стоимость и большое количество внешних выводов микропроцессора. При использованиии двух шин для передачи команд и данных, микропроцессор должен иметь почти вдвое больше выводов, так как шина адреса и шина данных составляют основную часть выводов микропроцессора. Для уменьшения количества выводов кристалла микропроцессора фирмы-производители микросхем объединили шины данных и шины адреса для внешней памяти данных и программ, оставив только различные сигналы управления (WR, RD, IRQ) а внутри микропроцессора сохранили классическую гарвардскую архитектуру. Такое решение получило название модифицированная гарвардская архитектура.

Модифицированная гарвардская структура применяется в современных микросхемах сигнальных процессоров. Ещё дальше по пути уменьшения стоимости кристалла за счет уменьшения площади, занимаемой системными шинами пошли производители однокристалльных ЭВМ — микроконтроллеров. В этих микросхемах применяется одна системная шина для передачи команд и данных (модифицированная гарвардская архитектура) и внутри кристалла.

В сигнальных процессорах для реализации таких алгоритмах как быстрое преобразование Фурье и цифровая фильтрация часто требуется еще большее количество внутренних шин. Обычно применяются две шины для чтения данных, одна шина для записи данных и одна шина для чтения инструкций. Подобная структура микропроцессора получила название расширенной гарвардской архитектуры. Этот подход практикуют производители сигнальных процессоров — фирмы Analog Devices (семейства сигнальных процессоров BlackFin и Tiger Shark), Texas Instrunents (семейства сигнальных процессоров C5000™ DSPs и C6000™ DSPs), Freescale (семейства сигнальных процессоров MSC8251 и DSP56K).

Архитектура ЭВМ. Урок. «Архитектура Электронно Вычислительных Машин»

Ищем педагогов в команду «Инфоурок»

Реферат

Тема: ’’Архитектура ЭВМ и ее основные характеристики’’.

Введение

В своем историческом докладе, опубликованном в 1945 году, Джон фон Нейман выделил и детально описал пять ключевых компонентов того, что ныне называют » архитектурой фон Неймана » современного компьютера.

Фон Нейман отмечал, что эта система должна работать с двоичными числами, быть электронным, а не механическим устройством и выполнять операции последовательно, одну за другой.

Архитектура и структура ЭВМ

Структура компьютера — это совокупность его функциональных элементов и связей между ними. Элементами могут быть самые различные устройства — от основных логических узлов компьютера до простейших схем. Структура компьютера графически представляется в виде структурных схем, с помощью которых можно дать описание компьютера на любом уровне детализации.

Наиболее распространены следующие архитектурные решения.

Физически магистраль представляет собой многопроводную линию с гнездами для подключения электронных схем. Совокупность проводов магистрали разделяется на отдельные группы: шину адреса, шину данных и шину управления.

П

Контроллер — устройство, которое связывает периферийное оборудование или каналы связи с центральным процессором, освобождая процессор от непосредственного управления функционированием данного оборудования.

Архитектура многопроцессорного компьютера

Преимущество в быстродействии многопроцессорных и многомашинных вычислительных систем перед однопроцессорными очевидно.

Архитектура с параллельным процессором

В современных машинах часто присутствуют элементы различных типов архитектурных решений. Существуют и такие архитектурные решения, которые радикально отличаются от рассмотренных выше.

Современный персональный компьютер состоит из нескольких основных конструктивных компонентов:

Системный блок

В системном блоке размещаются:

Материнская плата

При нормальной работе материнской платы о ней не вспоминают, пока не понадобится усовершенствовать компьютер. Обычно хотят поставить более быстрый процессор, что и ведет к замене материнской платы. Нельзя, например, заменить старый Pentium MMX на Pentium III без новой материнской платы.

По размерам материнские платы в общем случае можно разделить на три группы. Раньше все материнские платы имели размеры 8,5/11 дюймов. В XT размеры увеличились на 1 дюйм в AT размеры возросли еще больше. Часто речь может идти о “зеленых” платах (green mothеrboard). Сейчас выпускаются только такие платы. Данные системные платы позволяют реализовать несколько экономичных режимов энергопотребления (в том числе, так называемый “sleep”, при котором отключается питание от компонентов компьютера, которые в данный момент не работают).

Американское агентство защиты окружающей среды (EPA) сосредоточила свое внимание на уменьшении потребления энергии компьютерными системами. Оборудование, удовлетворяющее ее (EPA) требованиям должно в среднем (в режиме холостого хода) потреблять не более 30Вт, не использовать токсичные материалы и допускать 100% утилизацию. Поскольку современные микропроцессоры используют напряжение питания 3,3-4В, а на плату подается 5В, на системных

платах монтируют преобразователи напряжение.

Частота процессора, системной шины и шин периферийных устройств

Быстродействие различных компонентов компьютера (процессора, оперативной памяти и контроллеров периферийных устройств) может существенно различаться. Для согласования быстродействия на системной плате устанавливаются специальные микросхемы (чипсеты), включающие в себя контроллер оперативной памяти (так называемый северный мост) и контроллер периферийных устройств (южный мост).

Рис.1. Логическая схема системной платы

Южный мост обеспечивает обмен информацией между северным мостом и портами для подключения периферийного оборудования.

Мышь и внешний модем подключаются к южному мосту с помощью последовательных портов, которые передают электрические импульсы, несущие информацию в машинном коде, последовательно один за другим. Обозначаются последовательные порты как COM1 и COM2, а

аппаратно реализуются с помощью 25-контактного и 9-контактного разъемов, которые выведены на заднюю панель системного блока.

Основные характеристики вычислительной техники

К основным характеристикам вычислительной техники относятся ее эксплуатационно-технические характеристики, такие, как быстродействие, емкость памяти, точность вычислений и др.

Быстродействие ЭВМ рассматривается в двух аспектах. С одной стороны, оно характеризуется количеством элементарных операций, выполняемых центральным процессором в секунду. Под элементарной операцией понимается любая простейшая операция типа сложения, пересылки, сравнения п т. д. С другой стороны, быстродействие ЭВМ существенно зависит от организации ее памяти. Время, затрачиваемое на поиск необходимой информации в памяти, заметно сказывается на быстродействии ЭВМ.

В зависимости от области применения выпускаются ЭВМ с быстродействием от нескольких сотен тысяч до миллиардов операций в секунду. Для решения сложных задач возможно объединение нескольких ЭВМ в единый вычислительный комплекс с требуемым суммарным быстродействием.

Емкость, или объем, памяти определяется максимальным количеством информации, которое можно разместить в памяти ЭВМ. Обычно емкость памяти измеряется в байтах. Как уже отмечалось, память ЭВМ подразделяется на внутреннюю и внешнюю. Внутренняя, или оперативная память, по своему объему у различных классов машин различна и определяется системой адресации ЭВМ. Емкость внешней памяти из-за блочной структуры и съемных конструкций накопителей практически неограничена.

Точность вычислений зависит от количества разрядов, используемых для представления одного числа. Современные ЭВМ комплектуются 32- или 64-разрядными микропроцессорами, что вполне достаточно для обеспечения высокой точности расчетов в самых разнообразных приложениях. Однако, если этого мало, можно использовать удвоенную или утроенную разрядную сетку.

Система команд — это перечень команд, которые способен выполнить процессор ЭВМ. Система команд устанавливает, какие конкретно операции может выполнять процессор, сколько операндов требуется указать в команде, какой вид (формат) должна иметь команда для ее распознания. Количество основных разновидностей команд невелико. С их помощью ЭВМ способны выполнять операции сложения, вычитания, умножения, деления, сравнения, записи в память, передачи числа из регистра в регистр, преобразования из одной системы счисления в другую и т. д. При необходимости выполняется модификация команд, учитывающая специфику вычислений. Обычно в ЭВМ используется от десятков до сотен команд (с учетом их модификации). На современном этапе развития вычислительной техники используются два основных подхода при формировании системы команд процессора. С одной стороны, это традиционный подход, связанный с разработкой процессоров с полным набором команд, — архитектура CISC (Complete Instruction Set Computer — компьютер с полным набором команд). С другой стороны, это реализация в ЭВМ сокращенного набора простейших, но часто употребляемых команд, что позволяет упростить аппаратные средства процессора и повысить его быстродействие — архитектура RISC (Reduced Instruction Set Computer — компьютер с сокращенным набором команд).

Стоимость ЭВМ зависит от множества факторов, в частности от быстродействия, емкости памяти, системы команд и т. д. Большое влияние на стоимость оказывает конкретная комплектация ЭВМ и, в первую очередь, внешние устройства, входящие в состав машины. Наконец, стоимость программного обеспечения ощутимо влияет на стоимость ЭВМ.

Надежность ЭВМ — это способность машины сохранять свои свойства при заданных условиях эксплуатации в течение определенного промежутка времени. Количественной оценкой надежности ЭВМ, содержащей элементы, отказ которых приводит к отказу всей машины, могут служить следующие показатели:

• вероятность безотказной работы за определенное время при данных условиях эксплуатации;

• наработка ЭВМ на отказ;

• среднее время восстановления машины и др.

Для более сложных структур типа вычислительного комплекса или системы понятие «отказ» не имеет смысла. В таких системах отказы отдельных элементов приводят к некоторому снижению эффективности функционирования, а не к полной потере работоспособности в целом.

Важное значение имеют и другие характеристики вычислительной техники, например: универсальность, программная совместимость, вес, габариты, энергопотребление и др. Они принимаются во внимание при оценивании конкретных сфер применения ЭВМ.

Список литературы

Информатика. Базовый курс

А. А. Смирнов Архитектура вычислительных систем, М. Наука, 1990

Архитектура компьютера. Цифровой логический уровень

Компьютер — это машина, которая может выполнять вычисления через исполнение примитивных операций. Она может понимать только два сигнала, которые принимаются за 0 и 1.

Организация архитектур машин представляется как ряд уровней, каждый из которых надстраивается над нижележащим уровнем. Это сделано не просто так, с помощью многоуровневой архитектуры мы можем абстрагироваться от реализации и сложности нижнего уровня, тем, самым облегчить процесс проектирования, и уменьшить вероятность ошибок. Абстрагирование является ключевым моментом во всей архитектуре компьютера.

Организация компьютера состоит из 6 уровней: цифровой логический, микроархитектура, архитектура набора команд (ISA), операционная система, язык ассемблера, прикладной, конечно, если не считать физический уровень, который находится ниже цифрового логического уровня. У меня нет пока что в планах рассказывать все, что происходит выше уровня ISA. На это есть две причины: во-первых, цель этих статей заключается не в том, чтобы рассмотреть все уровни, а в том, чтобы показать, что из себя представляют уровни 0-2, и, во-вторых, на habr’е существует немало статей по уровням выше ISA и без меня. В этой статье будет показан цифровой логический уровень, а в следующих двух микроархитектура и архитектура набора команд соответственно.

Цифровой логический уровень

Цифровой логический уровень по сути представляет собой набор логических функций, которые взаимодействую между собой для выполнения большей задачи. Вся работа этого уровня заключается в двух базовых концепциях: вентили и булева алгебра. Сначала я расскажу про них, а дальше про логические схемы и то как они используются при разработке, и в заключении, то что из себя представляет память и как она реализуется.

Вентиль

Вентиль (рис. 1.0) является устройством, которое принимает входные сигналы и выдает выходные, сам он реализован на транзисторах (об их работе я рассказывать не буду). Вентили используются на данном уровне как «строительный» материал, чтобы представлять базовые логические операции, а дальше уже идет их комбинирование для реализации тех или иных схем, то есть смысл данного уровня заключается в построении переиспользуемых схем, а не о работе вентилей (и транзисторов); дальше уже на основе этих схем могут быть построены более сложные и узкоспециализированные схемы, например, целые модули памяти, различная логика, например, для того как будут взаимодействовать компоненты CPU на уровне микроархитектуры и тд.

Рисунок 1.0. Изображение вентилей.

Таблица 1.0. Таблица истинности для основных операций.

| A | B | И | И-НЕ | ИЛИ | ИЛИ-НЕ | ИСК-ИЛИ |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 |

Булева алгебра

Этот вид алгебры работает с 0 и 1, здесь присутствуют такие операции (табл. 1.0) как: И (конъюнкция), ИЛИ (дизъюнкция), НЕ (отрицание), ИСКЛЮЧАЮЩЕЕ ИЛИ и их комбинации и т.д. Чтобы описать логические функции можно использовать разные способы, но мы сконцентрируемся только на двух: таблица истинности и дизъюнктивно нормальная форма.

Для построения таблицы истинности мы просто перебираем все комбинации значений всех переменных. Таблица позволяет увидеть нам все возможные комбинации при которых функция принимает значения истины или лжи, она подходит, когда нам необходимо такое свойтсво, например, декодер. Дизъюнктивно нормальная форма позволяет нам сократить ее размеры таблицы, для этого, мы используем только те комбинации значений переменных при которых функция принимает только истинные значения. Чтобы создать схему, которая будет принимать истинное значение только с нужными нам комбинациями, нам необходимо представить эти строки в виде минтерм.

Рисунок 1.1. Схема ИСКЛЮЧАЮЩЕГО ИЛИ (черта над переменной обозначает НЕ).

Логические схемы

Логическая схема — это набор объединенных вентилей с входными и выходными сигналами. На рис 1.1 тоже изображена схема у которой входными сигналами являются A и B, выходной сигнал идет от операции ИЛИ; также у нее есть три вентиля: два И, один ИЛИ. Теперь давайте рассмотрим некоторые виды схем с которыми нам потребуется встречаться в дальнейшем, к ним относятся: комбинационные, арифметические, интегральные схемы.

Комбинационные схемы

Комбинационная схема — это схема с одним дополнительным свойством: значения выходных сигналов зависят только от входных, или другими словами, в ней нет никаких запоминающих устройств. Из этого вида схем создаются переиспользуемые компоненты, которые применяются для реализации большинства других схем, мы рассмотрим несколько, а именно: компаратор, декодер, мультиплексор/демультиплексор.

Компаратор имеет n входных парных линий (то есть 2n входов) и одну выходную линию. Логика его работы заключается в том, чтобы сравнить каждую пару битов (биты слова A сравниваются с соответствующими битами слова B) и при неравенстве хоть одной из них выдать 0 (если за ложь принят 0), иначе 1. Давайте построим таблицу истинности (табл. 1.1) для однобитного компаратора; можно заметить, что она равна таблице истинности ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ (когда к операции добавлен НЕ, то все выходные значения в таблице становятся противоположными). Теперь давайте расширим его до двухбитного компаратора, построим таблицу истинности (табл. 1.2) для него от двух переменных значения которых зависит от двух однобитных компаратора, то есть от двух ИСКЛЮЧАЮЩЕГО ИЛИ-НЕ; в ней значение 1 в CMP0 (и CMP1) значит, что два входа какото-то компаратора равны, 0 наоборот, то есть 1 в столбце R должна быть только, когда значения равны в двух компараторах. Эта таблица истинности совпадает с таблицей И, то есть мы объединяем все ИСКЛЮЧАЮЩЕГО ИЛИ-НЕ операцией И и у нас получится двухбитный компаратор (рис. 1.3а). Для дальнейшего расширение компаратора необходимо лишь добавить ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и подсоединить его к И. Недостаток такой реализации заключается в ее избыточности, нам требуется добавлять вентили НЕ для каждого ИСКЛЮЧАЮЩЕГО ИЛИ; мы можем от этого избавится (рис. 1.3б), если заменим вентиль И с НЕ входами на ИЛИ-НЕ, так как их таблицы истинности совпадают.

Таблица. 1.1. Таблица истинности для однобитного компаратора.

Рисунок 1.3. Две схемы двухбитных компараторов.

Декодер обладает n входными линиями, 2^n выходными, он реализован так, чтобы сигнал (истинна, 1) прошел только в одну выходную линию. Каждый выходной вентиль И получает свою комбинацию значений переменных, которые (значения) находятся в какой-то строке таблицы истинности, а как мы уже знаем, строку таблицы истинности можно реализовать как минтерму, то есть мы каждую строку представляем как вентиль И (рис. 1.4) от нескольких переменных. Основное применение декодера заключается в выборочном включении разных частей схемы (или схем), например, у АЛУ (о нем далее) имеется несколько операции, которые он может выполнять над входными значениями, чтобы их выбрать одну из них используется декодер.

Рисунок 1.4 Декодер.

Мультиплексор обладает 2^n входными линиями, n линиями управления и одной выходной линией. Он в реализации в какой-то степени похож (рис 1.5) на декодер, если представить входы декодера как линии управления, дополнить каждый вентиль И дополнительным входным сигналом и объединить выходные значения всех И одним ИЛИ. Суть его работы заключается в том, чтобы на выход поступал сигнал только от одной из возможных входных линий. Мультиплексор применяется в разных целях, например, он может пригодиться для преобразования параллельного кода в последовательный. Допустим у нас есть параллельная (это значит, что линии работают одновременно) шина с несколькими линиями по которым параллельно передаются биты; чтобы считать нужное нам слово (обычно разрядность слова соответствует разрядности регистра в процессоре) мы соединяем линий шины с входами мультиплексора и последовательно включаем по одному входу, допустим сверху вниз, тем самым на выход у нас пойдет точная последовательность битов.

Демультиплексор является обратным мультиплексору, он имеет одну входную линию, n линий управления и 2^n выходных линий. Логика его работы точно такая же как и в мультиплексоре, только один входной сигнал идет в один из выходных. Может быть использован для преобразования последовательного кода в параллельный.

Рисунок 1.5. Мультиплексор.

Арифметические схема

Данный вид схем выполняет арифметические операции над входными сигналами. Основными схемами являются: логические функции, сумматор, схема сдвига, АЛУ (ALU, Arithmetic Logic Unit).

Полусумматор и полный сумматор

Полусумматор состоит из двух входных и двух выходных линий, Полусумматор является простой схемой (рис. 1.6) из двух вентилей: И и ИСКЛЮЧАЮЩЕЕ ИЛИ. Сам по себе полусумматор может складывать только одноразрядные значения, но зачем же тогда нам нужен полный сумматор? В основном мы хотим складывать значения с большей разрядностью, но только одним полусумматором мы удовлетворить это желание не может. Когда мы складываем два одноразрядных значения, то у нас может произойти переполнение (табл. 1.3 последняя строка истинности в столбике перенос). Это когда результат операции не помещается в той разрядности, которой обладают входные элементы (в данном случае 1). При сложении двух единиц получает двойка, которую нельзя сохранить в одном бите, поэтому необходимо перенести его, чтобы воспользоваться при дальнейших вычислениях, но так как в полусумматоре не предусмотрена возможность использования двух значений и переноса одновременно, то складывать значения с разрядностью более чем единицу не получится. Например, допустим мы складываем два 3-разрядных числа, 5 (101 в двоичной) и 7 (111 в двоичной), сложение двух чисел начинается с младших разрядов, на входы полусумматора направляются 1 и 1, на выходе суммы получаем 0 и на выходе переноса 1, вот здесь и возникает проблема, следующие значения, которые должны пойти в полусумматор, это 0 и 1 соответственно, но, что делать с переносом, ведь для него нет никакого свободного входа, а отброс ить его нельзя, поэтому полусумматоры не могут напрямую использоваться для сложений.

У полного сумматора есть (рис. 1.7) три входных линии и две выходные линии. Входной перенос, как и выходной, используется для возможности объединения сумматоров в один с большей разрядностью. Сумматор состоит из двух полусумматоров, чтобы построить сумматор большей разрядности, необходимо только объединить сумматоры через входные и выходные переносы.

Рисунок 1.6. Схема полусумматор.

Таблица 1.3. Таблица истинности полусумматора.

Рисунок 1.7. Схема полного сумматора.

Таблица 1.4. Таблица истинности полного сумматора.

| A | B | Вход перенос | Сумма | Выход перенос |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

Сдвиг необходим для того, чтобы, например, выполнять умножение (сдвиг влево) и деление (сдвиг вправо), но только с числами, которые являются степенью двойки (1, 2, 4, 8 и тд). Схема сдвига (рис. 1.8) должна выполнять смещение на одну позицию влево или вправо в зависимости от бита направления. Бит направления (С) в зависимости от своего значения включает те или иные вентили И. Если он равен 0 (сдвиг влево), то сигнал который идет напрямую (то есть не проходит через НЕ) будет выключать вентиль который находятся выше в паре из двух вентилей И и один крайний вентиль И снизу. Сигнал, который проходит через НЕ, будет включать нижние вентиль в паре из двух вентилей И и один крайний вентиль И сверху. Это значит, что входные значения In будут выходить только из вентилей И выходные сигналы, которых направлены в нижнюю сторону; старший бит (I3) будет утерян, так как самый нижний вентиль И не пропустит входной сигнал дальше. Аналогичная ситуация происходит, когда бит направления равен 1 (сдвиг вправо), только теперь будут включены другие вентили И и сигнал уже будет направлен в противоположную (в данной реализации) сторону, и, следовательно, произойдет сдвиг вправо.

Рисунок 1.8. Схема сдвига.

Арифметико Логическое Устройство

АЛУ — это схема (рис. 1.9), которая содержит в себе множество арифметических схем, она предназначена для того, чтобы в одном месте хранить все операции необходимые для какой-либо цели. Реализация АЛУ разделяется на несколько частей (в данной реализации): распространение входных операндов, логические функции, сумматор и мультиплексор. Как мы помним декодер должен выполнять«включение» операций, но здесь я решил сделать мультиплексор, который подает на выход «Результат» значение, только одной из четырех операций; два нижних вентиля И в нем делят одну и ту же комбинацию при которой мультиплексор работает, это необходимо потому, что «Выход переноса» и «Сумма» сумматора являются частью одной операции, то есть оба этих входа должны работать только когда выбрано суммирование. Наш АЛУ предназначен для работы с одноразрядными значениями, но его можно почти без проблем изменить на большую разрядность. Входные линии INA и INB предназначены для включения/выключения A и B соответственно.

Рисунок 1.9. Схема АЛУ.

Интегральные схемы

Также известна как микросхема, это те же схемы показанные выше, только они помещены в корпус, который определяет, то где должны находится выводы для сигналов. Этот вид схем возник из-за того, что продавать отдельные схемы и вентили не очень целесообразно: по крайне мере из-за того, что нет стандарта, который бы говорил как, где и в каком кол-ве должны располагаться входные и выходные сигналы.

Есть куча разных видов корпусов, но мы рассмотрим наиболее известные:

Память

У памяти выходные значения зависят не только от входных, то есть она способна запоминать. Концептуально все схемы памяти похожи (рис. 2.1), память может «запоминать» благодаря тому, что она «замкнута», то есть верхний вентиль зависит от выходного значения нижнего, а нижний зависит от выходного значения верхнего.

Рисунок 2.1. SR защелка.

Таблица 1.6. Таблица истинности SR защелки.

Когда мы подаем на входы S, R сигналы 0, а в Q хранится значение 0, то в верхний вентиль ИЛИ НЕ поступают два нуля 0, на выходе у него будет 1 (табл. 1.0). Далее в нижний вентиль ИЛИ-НЕ поступают 0 и 1, на выходе будет 0; то есть у нас получилось не противоречивое состояние защелки (рис. 2.2a). В данном случае выходное значение защелки равно 0 (Q), то есть она хранит значение 0.

В ином варианте мы можем подать на входы S, R сигналы 0, а в Q хранится значение 1. В верхний вентиль ИЛИ-НЕ поступают 0 и 1, что на выходе дает 0. В нижний вентиль ИЛИ-НЕ поступают 0 и 0, на выходе будет 1; Снова мы попали в не противоречивое состояние защелки (рис. 2.2б). Выходное значение защелки равно 1.

Рисунок 2.2. Два возможных корректных состояния SR защелки.