что такое кольцевая шина процессора

Железный сайт

Совсем недавно компания AMD предложила систему команд SSE5. Однако Intel решили создать свою собственную реализацию SSE5, которая получила название AVX (Advanced Vector Extensions).

Данные инструкции представляют собой дальнейшее развитие SSE и используют те же операции SIMD (Single Instruction, Multiple Data), ведущих свое начало с системы команд MMX. Только в AVX для ускорения обработки данных увеличена разрядность операций. Система команд AVX добавляет 12 новых инструкций и увеличивает размер регистров XMM со 128 бит до 256 бит.

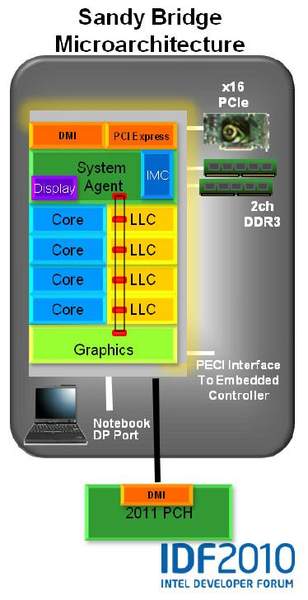

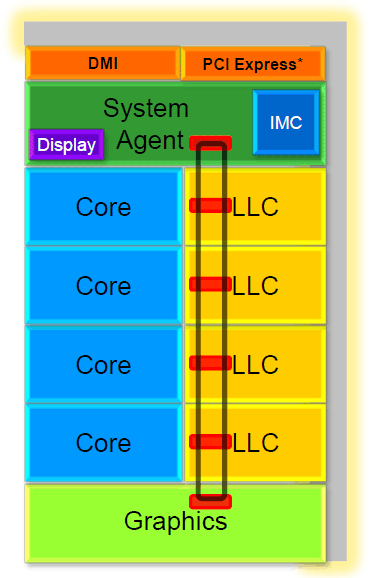

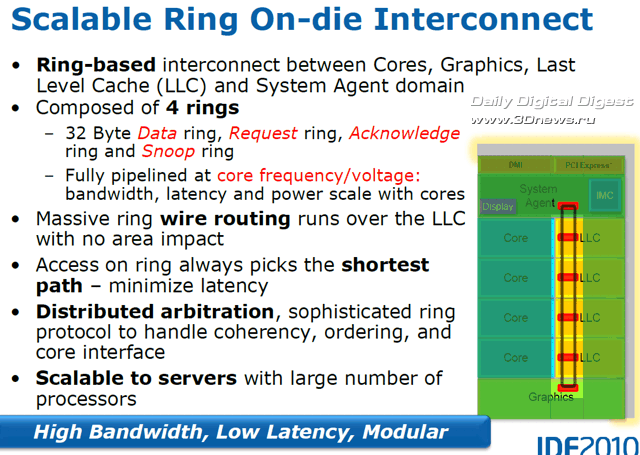

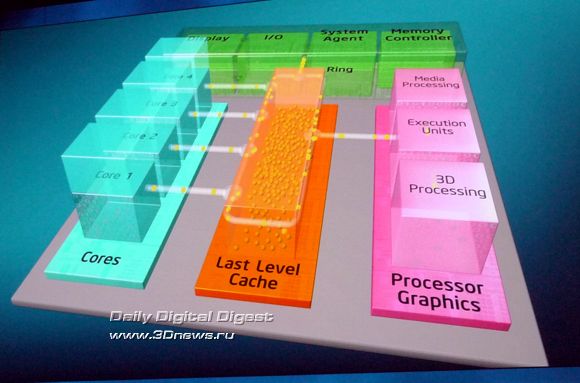

Для обмена данными между внутренними компонентами CPU в архитектуре Sandy Bridge предусмотрена кольцевая шина. Упрощенно ее можно описать следующим образом. Когда компонент хочет «общаться» с другим компонентом, он помещает информацию в кольцевую шину, а она перемещает эту информацию адресату. Компоненты не «говорят» непосредственно друг с другом, они должны использовать кольцо. Кольцевая шина используется для общения между ключевыми компонентами процессора. Это ядра CPU, кэш-память L3 (теперь называется кеш-память последнего уровня или LLC), а также System Agent (в него входят интегрированный контроллер памяти, контроллер PCI Express, блок управления питанием и дисплей) и графическое ядро.

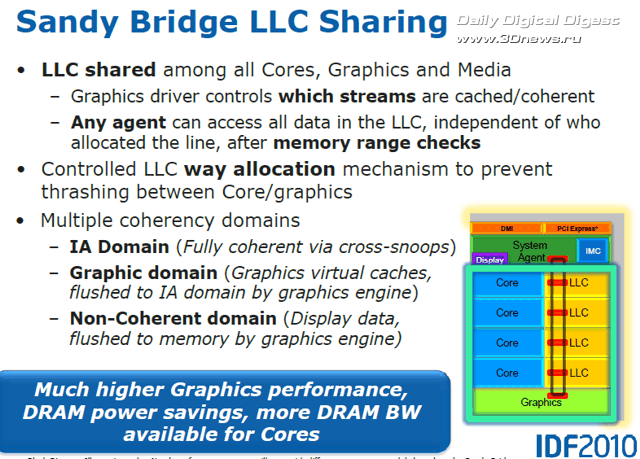

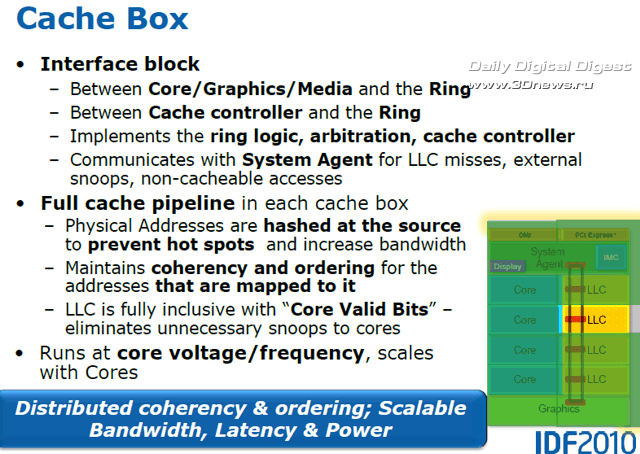

На рисунке ниже Вы можете видеть схему кольцевой шины (черный овал) с ее «остановками» (красные прямоугольники). Доступ к кешу L3 имеют не только процессорные ядра, но также графическое ядро и system agent. Каждое процессорное ядро имеет прямой доступ к своему сегменту кеша L3. Все сегменты кеша L3 имеют контроллер доступа к кольцевой шине.

Кроме того, ядра CPU не привязаны в определенному сегменту кеша. Любое ядро может использовать любой из кешей. На рисунке ниже изображен четырехъядерный CPU с четырьмя сегментами L3. Так, например, Core 1 может обращаться не только к кешу 1, а к любому. То есть любое ядро процессора может получить доступ данным, которые хранятся в любом из кешей.

Кольцевая шина включает фактически четыре 32-х байт колец: шина данных (Data Ring), шина запросов (Request Ring), шина подтверждения (Acknowledge Ring) и шина мониторинга (Snoop Ring). Все они работают на тактовой частоте процессора. Передача данных между ними основана на протоколе QPI (QuickPath Interconnect), который используется в CPU LGA 1366 для обмена данными с чипсетом.

Каждый компонент решает, нужно ли ему использовать кольцевую шину, если она свободна. Кольцо всегда выбирает кратчайший путь к месту назначения.

Процессоры Intel Sandy Bridge — все секреты

Оглавление

В скобках указаны значения для Nehalem (если есть отличие).

| Кэш | L0m (новый) | L1I | L1D | L2 | L3 |

| Размер | 1536 мопов | 32 КБ | 256 КБ | 1–20 (2–30) МБ | |

| Ассоциативность | 8 | 8 (4) | 8 | 8 | 8, 12, 16, 20 (12, 16, 24) |

| Размер строки | 6 мопов | 64 байта | |||

| Задержка, тактов | 3? | 4 | 4–7 (4) | 11–12 (10) | ≈26–31 (≈35–40) |

| Число портов | 2 | 1 | 3 (2) | 1 | 1 на банк, 2–8 банков (2 на кэш, 1–10 банков) |

| Разрядность портов | 4 мопа | 16 байт | 64 байта | 64? (32) байта | |

| Частота (f — частота ядра) | f | f/2 | Максимум всех f (2,13–2,66 ГГц) | ||

| Политика работы | Включающая | Включающая | |||

| Свободная | |||||

| Только чтение | Отложенная запись | ||||

| Общий для … | Потоков ядра | Всех ядер, включая ГП | |||

Сразу скажем, что кэши L1I и L2 почти не изменились — у первого ассоциативность снова (как и до Nehalem) стала 8, а у второго чуть увеличилась задержка. Самое главное изменение в ядрах, касаемое кэшей, кроется в доступе к L1D, который теперь стал 3-портовым: к раздельным портам чтения и записи добавили ещё один для чтения. Кроме того, как уже было указано, в планировщике Nehalem 2-й порт вычисляет адрес чтения и исполняет само чтение, 3-й вычисляет адрес записи (только), а 4-й — исполняет саму запись. В SB же порты 2 и 3 могут и вычислить любой адрес, и исполнить чтение.

Внимательный Читатель сразу найдёт подвох: портов L1D — 3, а адресных генераторов — 2. При не более чем 16-байтовых обменах их устоявшийся максимальный темп составит 32 байта/такт (либо два чтения, либо чтение и запись). 32-байтовые операции каждым портом обслуживаются за два такта, причём вычисление адреса для конкретной команды происходит в течение первого из них. Так что для двух чтений и одной записи требуется три адреса в течение двух тактов — тогда при потоковых обменах один из трёх нужных адресов можно вычислить заранее в течение второго такта предыдущей 32-байтовой операции. Только так мы получим искомый максимум в 48 байт/такт.

Возникает довольно странный компромисс: три 16-байтовые операции за такт в потоке сделать нельзя. С другой стороны, за такт можно вычислить адреса для двух 32-байтовых обменов, но даже одно 32-байтовое чтение за такт не запустишь, потому что порты чтения не объединяются. Т. е. либо нам не будет хватать числа AGU (тех, что в портах 2 и 3), либо ширины портов, либо возможности их объединения.

Как мы знаем из теории, многопортовость в кэшах чаще всего делается не явная, а мнимая, с помощью многобанковости. Однако Nehalem нарушил это правило, внедрив 8-транзисторные битовые ячейки для всех кэшей ядра. Помимо большей экономии (об этом подробно рассказывалось в статье о микроархитектуре Intel Atom, который тоже применяет такую схему), это также даёт возможность получить истинную 2-портовость (чтение + запись), что и было использовано в L1D — никаких конфликтов по адресам в имеющихся 8 банках не было. В SB банков по-прежнему 8, а портов уже 3. Очевидно, конфликты неизбежны, но только среди адресов портов чтения.

Каждый банк L1D имеет ширину в 8 байт, вместе составляя строку, поэтому каждый из 16-байтовых портов использует 1–2 банка при выровненном доступе и 2–3 при невыровненном. Например, 8-байтовое чтение, пересекающее 8-байтовую границу, использует 2 банка, как и выровненное 16-байтовое. В SB конфликт происходит, если хоть один из банков, нужных одному чтению, также нужен и второму, причём для доступа к другой строке. Последнее означает, что если оба чтения требуют не только одинаковый(ые) банк(и), но и одинаковые номера строк в нём (них), то конфликта не будет, т. к. фактический доступ произойдёт один, и он обслужит оба обращения. В Nehalem, с его единственным чтением за такт, такого, очевидно, быть не могло.

Упомянув о невыровненном доступе, скажем и о более «грешных» делах — пересечении строки кэша, что обойдётся 5-тактным штрафом, и границы страницы виртуальной памяти (чаще всего — 4 КБ), что наказывается в среднем 24 тактами (ситуация требует сериализации конвейера). Причём последняя цифра малообъяснима, т. к. TLB, как мы увидим ниже, способны на одновременную обработку обеих смежных страниц — но даже при последовательном доступе двухзначной цифры получиться не может…

Изменений в LSU (контроллере L1D, который Intel упорно называет MOB) не меньше, чем в само́м кэше. Начнём с того, что очередь чтения удлинилась с 48 до 64 ячеек, а записи — с 32 до 36. Каждая ячейка привязана к одному мопу, а очередь записи хранит ещё и 32 байта данных (было 16). Очередь чтения хранит все команды считываний, но в каждый момент не более 32 могут обрабатываться на разных стадиях. Фактически, это отдельные диспетчер и планировщик, «ROB» которых хранит 64 мопа, а «резервация» — 32. Когда чтение завершено, моп удаляется из этой резервации, но остаётся в очереди чтения до отставки. Очередь записи хранит информацию до отставки предыдущих команд, когда ясно, что адрес, данные и сам факт исполнения команды верны, а значит её можно попытаться записать в кэш. Если попытка успешна — моп записи уходит в отставку, освобождая место и в очереди, и в ROB. При промахе или других проблемах запись задержится.

Как и все современные кэши, L1D является неблокирующим — после промаха он может принимать дальнейшие запросы одновременно с заполнением себя подгруженными данными. Кэш может выдержать даже 3 промаха/такт. Одновременно удерживается столько промахов, сколько имеется буферов заполнения. В SB, как и в его предшественнике, у L1D таковых 10, а у L2 — 16. Политика отложенной записи в L1D и L2 означает, что модифицированная строка остаётся в кэше до вытеснения, однако информация о факте её модификации (если до этого данные были «свежие») отправляется в теги соответствующей строки в L3.

Внеочерёдный доступ

Внеочерёдный движок получил любопытное дополнение: предсказание адресов, на основе которого порядок обращений в кэш может быть переставлен, делается не отдельными адресами, а целыми диапазонами — предсказывается верхнее и нижнее значения адреса, в пределах которых, как предполагается, произойдёт запись. Если точно известный адрес чтения не попадает ни в один диапазон ещё не исполненных записей — чтение можно запустить заранее. Такой вариант срабатывает чаще имевшегося ранее, который разрешал внеочерёдную загрузку, только если есть высокая вероятность несовпадения с конкретным адресом записи. Сама вероятность рассчитывается, как в предсказателе переходов — в LSU, видимо, есть некий аналог таблицы BHT со счётчиком вероятности в каждой ячейке. Когда адрес записи становится известен, счётчик увеличивается при несовпадении адресов и уменьшается при конфликте.

Однако предсказатель оперирует только выровненными на 16 байт чтениями размером до 16 байт, а также выровненными 32-байтовыми — остальные будут ждать вычисления адресов всех предыдущих записей. Ещё одна проблема нового движка в том, что он предсказывает лишь младшие 12 бит адресов: если у записи и чтения они равны (даже если они не предсказаны, а точно известны), то чтение считается зависимым от записи. Т. е. фактически предсказывается лишь 8 бит адреса — с 5-го по 12-й. Возможно, ложная зависимость обусловлена тем, что в ячейках таблицы счётчиков нет поля, хранящего старшую часть адреса.

Ясно, что STLF не может работать одновременно с внеочерёдной загрузкой: адреса записей должны быть известны точно, а не только 8 битами.

Процессоры Intel. Внутренняя кольцевая шина (ring bus) и топология сетки (mesh).

Процессоры Intel. Внутренняя кольцевая шина (ring bus) и топология сетки (mesh).

Рис. 1. Каждый процессор обслуживался двумя кольцевыми шинами.

Процессоры Skylake-SP и Skylake-X используют топологию сетки (mesh) для связи ядер. Кэш L3, контролеры памяти и ввода/вывода тоже интегрируются в сетку. В результате можно легко наращивать число ядер процессора, сочетая высокую пропускную способность и низкие задержки. Технология для Intel не новая, поскольку она уже использовалась в вычислительных ускорителях Xeon Phi.

При переходе на топологию сетки Intel пришлось изменить расположение контроллеров памяти. Раньше они располагались ниже ядер, теперь вынесены в правую и левую часть. Все это обеспечивает более эффективную работу с памятью (рис. 3).

Тесты покажут, насколько существенно Intel смогла увеличить производительность благодаря переходу на сетчатую топологию в многопоточных приложениях. В теории новая топология обеспечивает большую пропускную способность по сравнению с кольцевой шиной, а также меньшие задержки, что должно увеличить производительность.

Ещё в марте 2017 года компания Intel показала изображение 28-ядерного кристалла процессора Skylake-SP. Тогда все обратили внимание, что расположение ядер и интерфейсов претерпели значительные изменения. Как выяснилось, в дальнейшем Intel откажется (и уже отказалась для процессоров Skylake в версиях Xeon и настольных решений высшей производительности) от внутрипроцессорной кольцевой шины.

Рис. 2. Intel Xeon Processor E5 v4 Product Family HCC.

Кольцевая шина (ring bus) была представлена еще в 2008 году вместе с архитектурой Nehalem и процессорами Westmere-EX. Она была необходима в связи с увеличением числа ядер на кристалле. Разработчики Intel использовали три варианта дизайна процессоров (в зависимости от максимального числа ядер на кристалле) с тремя вариантами кольцевой шины. В самом сложном случае процессор внутри разделялся на два кластера, каждый из которых обслуживался двумя кольцевыми шинами (рис. 2). Между собой шины соединялись двунаправленными коммутаторами с буферизацией (на диаграмме выше обозначены серым цветом).

Кольцевая шина, как вы можете знать, в максимальной конфигурации представляет собой четыре двунаправленных кольца (по два кольца на кластер из ядер), соединённых двумя двунаправленными коммутаторами с буферами. Дальнейшее наращивания числа ядер, кластеров и коммутаторов значительно увеличивает потребление и задержки при обмене данными между ядрами из разных кластеров. Выход найден в переходе на ячеистую сеть, в которой каждое ядро поддержано собственным коммутатором и возможностью координатной пересылки данных фактически напрямую любому другому ядру в процессоре.

Ранее подобную сеть Intel реализовала в архитектуре процессоров Xeon Phi (Knights Landing и другие), так что разработка опробована на практике и показала свою эффективность, ведь в составе ускорителей и процессоров Xeon Phi может быть свыше 70 ядер.

Рис. 3. Структура ячеистой сети.

Архитектура ячеистой 2D-сети дебютировала в продуктах Intel Knights Landing. Сеть состоит из горизонтальных и вертикальных межсоединений между ядрами, кэшем и контроллерами ввода-вывода. На схеме отсутствуют буферизированные переключатели, которые очень негативно сказываются на задержках. Возможность «ступенчатого» движения данных через ядра позволяет осуществлять гораздо более сложную и предположительно эффективную маршрутизацию. Intel утверждает, что 2D-сеть имеет более низкое напряжение и частоту, чем у кольцевой шины, но при этом обеспечивает более высокую пропускную способность и более низкую задержку.

Что такое кольцевая шина процессора

Ещё в марте компания Intel показала изображение 28-ядерного кристалла процессора Skylake-SP. Тогда мы обратили внимание, что расположение ядер и интерфейсов претерпели значительные изменения. Вчера в компании Intel на одном из домашних мероприятий пояснили, с чем связаны эти перемены в дизайне. Как выяснилось, в дальнейшем Intel откажется (и уже отказалась для процессоров Skylake в версиях Xeon и настольных решений высшей производительности) от внутрипроцессорной кольцевой шины.

реклама

Кольцевая шина (ring bus) была представлена в 2008 году вместе с архитектурой Nehalem и процессорами Westmere-EX. Она была необходима в связи с увеличением числа ядер на кристалле. Разработчики Intel использовали три варианта дизайна процессоров (в зависимости от максимального числа ядер на кристалле) с тремя вариантами кольцевой шины. В самом сложном случае процессор внутри разделялся на два кластера, каждый из которых обслуживался двумя кольцевыми шинами. Между собой шины соединялись двунаправленными коммутаторами с буферизацией (на диаграмме выше обозначены серым цветом).

По мере роста числа ядер кольцевая шина стала препятствием на пути увеличения пропускной способности и снижения задержек. Точнее, она стала слишком много потреблять, чтобы её можно было масштабировать в сторону увеличения скорости по обмену данными. Поэтому в процессорах Skylake-SP разработчики Intel решили применить иную структуру для связи ядер друг с другом — хорошо опробованную в архитектуре Intel Xeon Phi (Knights Landing) ячеистую сеть.

Каждое ядро в новой архитектуре имеет свой коммутатор с буфером и связано с любым другим ядром в составе процессора только через два узла — исходящий и входящий. Это позволяет ячеистой шине работать на относительно небольших частотах и существенно снизить общее потребление интерфейса без ухудшения пропускной способности и увеличения задержек. К тому же подобная структура коммуникаций очень хорошо масштабируется, позволяя Intel в будущем наращивать число ядер на кристалле без заметного увеличения энергетических затрат на внутреннюю транспортировку данных.

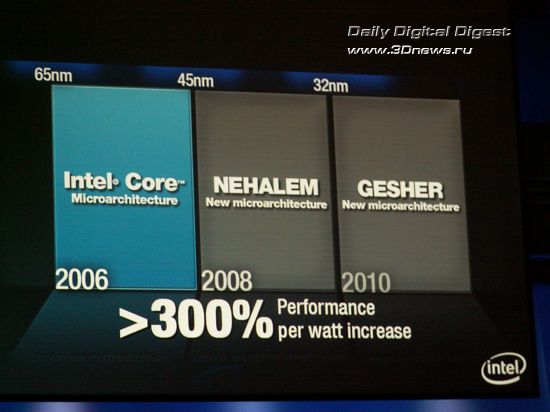

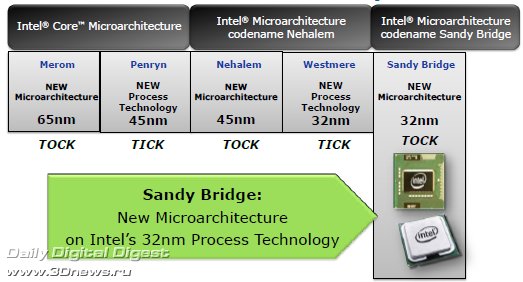

Микроархитектура Intel Sandy Bridge, часть I

Несколько лет назад, во времена господства бренда Pentium, первого появления торговой марки Intel Core и одноимённой микроархитектуры (Architecture 101), на слайдах о будущих процессорах впервые было упомянуто следующее поколение микроархитектуры Intel с рабочим названием Gesher («мост» на иврите), что чуть позже трансформировалось в Sandy Bridge.

Словом, когда трава была зелёная, а до Sandy Bridge было ещё как до Луны, уже тогда представители Intel говорили, что это будет совершенно новая процессорная микроархитектура. Именно так, cкажем, сегодня можно представить таинственную микроархитектуру Haswell, которая появится после поколения Ivy Bridge, которое, в свою очередь, придёт на смену Sandy Bridge в следующем году.

И всё же различия существенны. Настолько существенны, что теперь окончательно можно говорить о конце 15-летней эпохи микроархитектуры P6 (Pentium Pro) и о появлении нового поколения микроархитектуры Intel.

⇡#Микроархитектура Sandy Bridge: с высоты птичьего полёта

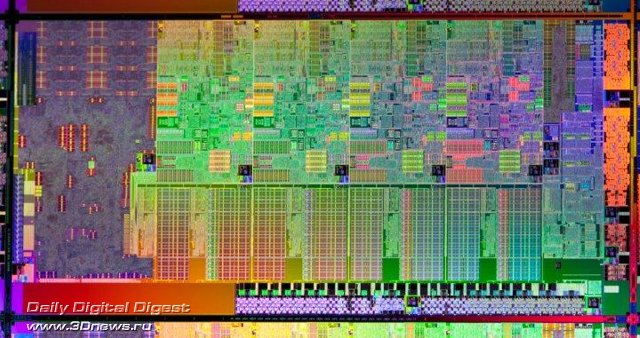

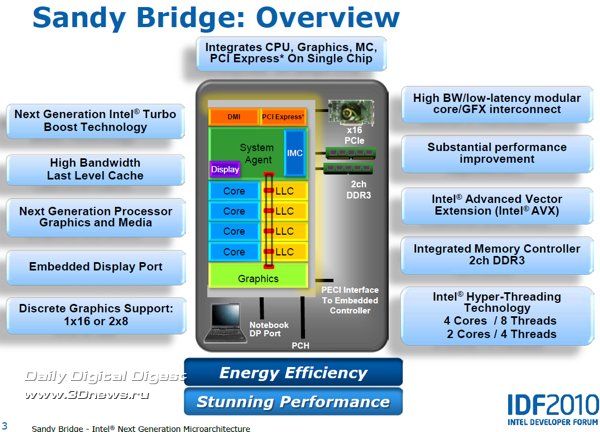

Чип Sandy Bridge – это четырёхъядерный 64-битный процессор с изменяемой (out-of-order) последовательностью исполнения команд, поддержкой двух потоков данных на ядро (HT), исполнением четырёх команд за такт; с интегрированным графическим ядром и интегрированным контроллером памяти DDR3; с новой кольцевой шиной, поддержкой 3- и 4-операндных (128/256-битных) векторных команд расширенного набора AVX (Advanced Vector Extensions); производство которого налажено на линиях с соблюдением норм современного 32-нм технологического процесса Intel.

Так, вкратце, одним предложением можно попробовать охарактеризовать новое поколение процессоров Intel Core II для мобильных и настольных систем, массовые поставки которых начнутся в самое ближайшее время.

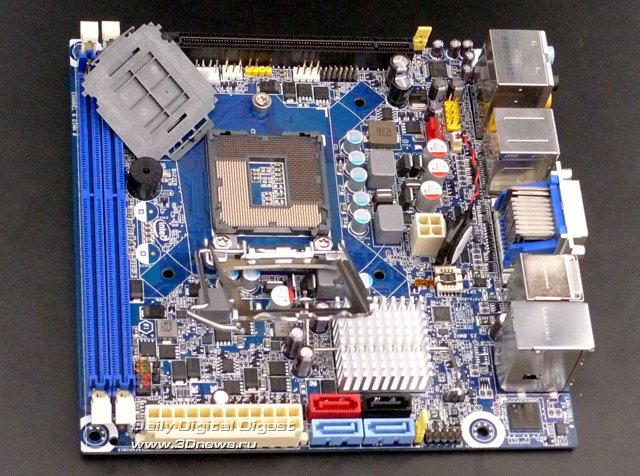

Процессоры Intel Core II на базе микроархитектуры Sandy Bridge будут поставляться в новом 1155-контактном конструктиве LGA1155 под новые системные платы на чипсетах Intel 6 Series.

Примерно такая же микроархитектура будет актуальна и для серверных решений Intel Sandy Bridge-EP, разве что с актуальными отличиями в виде большего количества процессорных ядер (до восьми), соответствующего процессорного разъёма LGA2011, большего объёма кеша L3, увеличенного количества контроллеров памяти DDR3 и поддержкой PCI-Express 3.0.

При создании архитектуры Sandy Bridge разработчики закончили начатый на этапе создания Arrandale/Clarkdale процесс интеграции и разместили все элементы на едином 32-нм кристалле, отказавшись при этом от классического вида шины QPI в пользу новой кольцевой шины. Суть микроархитектуры Sandy Bridge при этом осталась в рамках прежней идеологии Intel, которая делает ставку на увеличение суммарной производительности процессора за счёт улучшения «индивидуальной» эффективности каждого ядра.

Структуру чипа Sandy Bridge можно условно разделить на следующие основные элементы: процессорные ядра, графическое ядро, кеш-память L3 и так называемый «Системный агент» (System Agent).

В общем и целом структура микроархитектуры Sandy Bridge понятна. Наша сегодняшняя задача – выяснить назначение и особенности реализации каждого из элементов этой структуры.

⇡#Кольцевая шина (Ring Interconnect)

Кольцевая шина в версии архитектуры Sandy Bridge для настольных и мобильных систем (Core II) служит для обмена данными между шестью ключевыми компонентами чипа: четырьмя процессорными ядрами x86, графическим ядром, кешем L3 и системным агентом. Шина состоит из четырёх 32-байтных колец: шины данных (Data Ring), шины запросов (Request Ring), шины мониторинга состояния (Snoop Ring) и шины подтверждения (Acknowledge Ring), на практике это фактически позволяет делить доступ к 64-байтному интерфейсу кеша последнего уровня на два различных пакета. Управление шинами осуществляется с помощью коммуникационного протокола распределённого арбитража, при этом конвейерная обработка запросов происходит на тактовой частоте процессорных ядер, что придаёт архитектуре дополнительную гибкость при разгоне. Производительность кольцевой шины оценивается на уровне 96 Гбайт в секунду на соединение при тактовой частоте 3 ГГц, что фактически в четыре раза превышает показатели процессоров Intel предыдущего поколения.

Кольцевая топология и организация шин обеспечивает минимальную латентность при обработке запросов, максимальную производительность и отличную масштабируемость технологии для версий чипов с различным количеством ядер и других компонентов. По словам представителей компании, в перспективе к кольцевой шине может быть «подключено» до 20 процессорных ядер на кристалл, и подобный редизайн, как вы понимаете, может производиться очень быстро, в виде гибкой и оперативной реакции на текущие потребности рынка. Кроме того, физически кольцевая шина располагается непосредственно над блоками кеш-памяти L3 в верхнем уровне металлизации, что упрощает разводку дизайна и позволяет сделать чип более компактным.

Каждое из четырёх процессорных ядер имеет прямой доступ к «своему» сегменту кеша L3, при этом каждый сегмент кеша L3 предоставляет половину ширины своей шины для доступа кольцевой шины данных, при этом физическая адресация всех четырёх сегментов кеша обеспечивается единой хэш-функцией. Каждый сегмент кеша L3 обладает собственным независимым контроллером доступа к кольцевой шине, он отвечает за обработку запросов по размещению физических адресов. Кроме того, контроллер кеша постоянно взаимодействует с системным агентом на предмет неудачных обращений к L3, контроля межкомпонентного обмена данными и некешируемых обращений.

Дополнительные подробности о строении и особенностях функционирования кеш-памяти L3 процессоров Sandy Bridge будут появляться далее по тексту, в процессе знакомства с микроархитектурой, по мере возникновения необходимости.

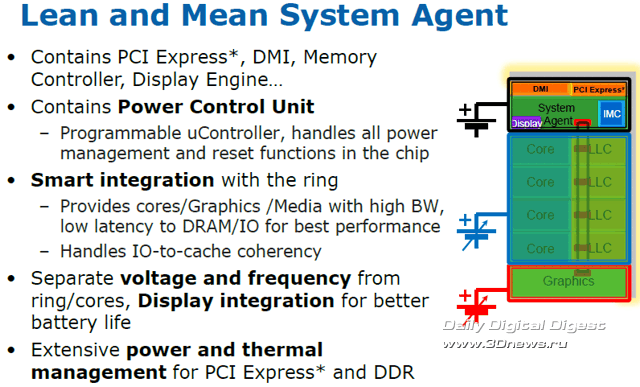

⇡#Системный агент: контроллер памяти DDR3, PCU и другие

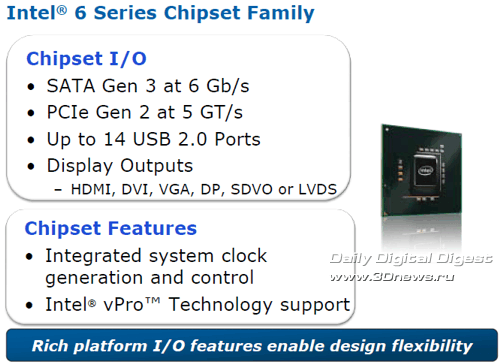

Системный агент микроархитектуры Sandy Bridge включает в себя контроллер памяти DDR3, модуль управления питанием (Power Control Unit, PCU), контроллеры PCI-Express 2.0, DMI, блок видеовыхода и пр. Как и все остальные элементы архитектуры, системный агент подключен в общую систему посредством высокопроизводительной кольцевой шины.

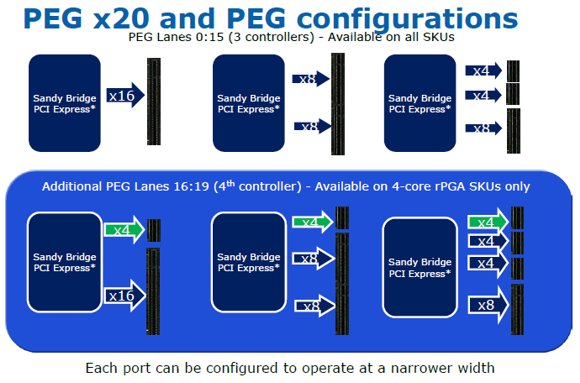

Архитектура стандартной версии системного агента Sandy Bridge подразумевает наличие 16 линий шины PCI-E 2.0, которые также могут быть распределены на две шины шины PCI-E 2.0 по 8 линий, или на одну шину PCI-E 2.0 на 8 линий и две шины PCI-E 2.0 по четыре линии. Двухканальный контроллер памяти DDR3 отныне «вернулся» на кристалл (в чипах Clarkdale он располагался вне процессорного кристалла) и, скорее всего, теперь будет обеспечивать значительно меньшую латентность.

Тот факт, что контроллер памяти в Sandy Bridge стал двухканальным, вряд ли обрадует тех, кто уже успел вывалить немалые суммы за оверклокерские комплекты трёхканальной памяти DDR3. Что ж, бывает, теперь будут актуальны наборы лишь из одного, двух или четырёх модулей.

По поводу возвращения к двухканальной схеме контроллера памяти у нас имеются кое-какие соображения. Возможно, в Intel начали подготовку микроархитектур к работе с памятью DDR4? Которая, из-за ухода от топологии «звезды» на топологию «точка-точка» в версиях для настольных и мобильных систем будут по определению только двухканальной (для серверов будут применяться специальные модули-мультиплексоры). Впрочем, это всего лишь догадки, для уверенных предположений пока что недостаточно информации о самом стандарте DDR4.

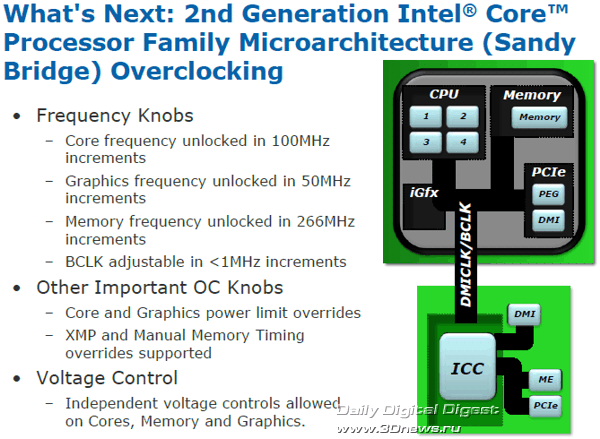

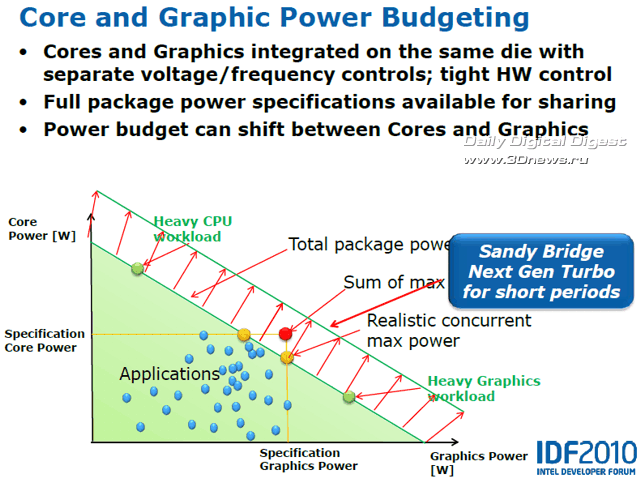

Расположенный в системном агенте контроллер управления питанием отвечает за своевременное динамичное масштабирование напряжений питания и тактовых частот процессорных ядер, графического ядра, кешей, контроллера памяти и интерфейсов. Что особенно важно подчеркнуть, управление питанием и тактовой частотой производится независимо для процессорных ядер и графического ядра.

Совершенно новая версия технологии Turbo Boost реализована не в последнюю очередь благодаря этому контроллеру управления питанием. Дело в том, что, в зависимости от текущего состояния системы и сложности решаемой задачи, микроархитектура Sandy Bridge позволяет технологии Turbo Boost «разогнать» ядра процессора и встроенную графику до уровня, значительно превышающего TDP на достаточно долгое время. И действительно, почему бы не воспользоваться такой возможностью штатно, пока система охлаждения ещё холодная и может обеспечить больший теплоотвод, чем уже разогретая?

Кроме того, что технология Turbo Boost позволяет теперь штатно «разгонять» все четыре ядра за пределы TDP, также стоит отметить, что управление производительностью и тепловым режимом графических ядер в чипах Arrandale/Clarkdale, по сути, только встроенных, но не до конца интегрированных в процессор, производилось с помощью драйвера. Теперь, в архитектуре Sandy Bridge, этот процесс также возложен на контроллер PCU. Такая плотная интеграция системы управления напряжением питания и частотами позволила реализовать на практике гораздо более агрессивные сценарии работы технологии Turbo Boost, когда и графика, и все четыре ядра процессора при необходимости и соблюдении определённых условий могут разом работать на повышенных тактовых частотах со значительным превышением TDP, но без каких-либо побочных последствий.

Принцип работы новой версии технологии Turbo Boost, реализованной в процессорах Sandy Bridge, отлично описывается в мультимедийной презентации, показанной в сентябре на Форуме Intel для разработчиков в Сан-Франциско. Представленный ниже видеоролик с записью этого момента презентации расскажет вам о Turbo Boost быстрее и лучше, чем любой пересказ.

Насколько эффективно эта технология будет работать в серийных процессорах, нам ещё предстоит узнать, но то, что показывали специалисты Intel во время закрытой демонстрации возможностей Sandy Bridge в дни IDF в Сан Франциско, просто поражает: и прирост тактовой частоты, и, соответственно, производительность процессора и графики, одномоментно могут достичь просто фантастических уровней.

Есть информация, что для штатных систем охлаждения режим такого «разгона» с помощью Turbo Boost и превышением TDP будет ограничен в BIOS периодом в 25 секунд. Но что если производители системных плат смогут гарантировать более качественный отвод тепла с помощью какой-нибудь экзотической системы охлаждения? Тут и открывается раздолье для оверклокеров…

Каждое из четырёх ядер Sandy Bridge может быть при необходимости независимо переведено в режим минимального энергопотребления, графическое ядро также можно перевести в очень экономичный режим. Кольцевая шина и кеш L3, в силу их распределения между другими ресурсами, не могут быть отключены, однако для кольцевой шины предусмотрен специальный экономичный ждущий режим, когда она не нагружена, а для кеш-памяти L3 применяется традиционная технология отключения неиспользуемых транзисторов, уже известная нам по предыдущим микроархитектурам. Таким образом, процессоры Sandy Bridge в составе мобильных ПК обеспечивают длительную автономную работу при питании от аккумулятора.

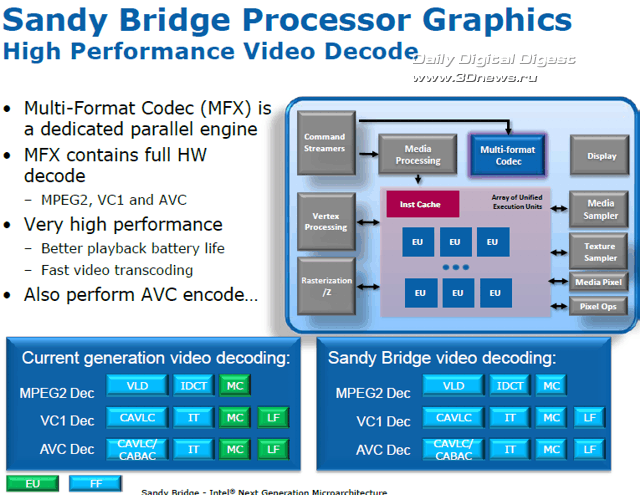

Модули видеовыхода и мультимедийного аппаратного декодирования также входят в число элементов системного агента. В отличие от предшественников, где аппаратное декодирование было возложено на графическое ядро (о его возможностях мы поговорим в следующий раз), в новой архитектуре для декодирования мультимедийных потоков используется отдельный, гораздо более производительный и экономичный модуль, и лишь в процессе кодирования (сжатия) мультимедийных данных используются возможности шейдерных блоков графического ядра и кеш L3.

В соответствии с современными веяниями, предусмотрены инструменты воспроизведения 3D-контента: аппаратный модуль декодирования Sandy Bridge способен без труда обрабатывать сразу два независимых потока MPEG2, VC1 или AVC в разрешении Full HD.

Сегодня мы познакомились со структурой нового поколения микроархитектуры Intel Core II с рабочим названием Sandy Bridge, разобрались со строением и принципом работы ряда ключевых элементов этой системы: кольцевой шины, кеш-памяти L3 и системного агента, в состав которого входит контроллер памяти DDR3, модуль управления питанием и другие компоненты.