что такое двухступенчатый триггер

Двухступенчатые триггеры

Рассмотренные синхронные триггеры являются одноступенчатыми. Условное обозначение одноступенчатых триггеров отображается символом T. Устойчивая работа таких триггеров в схемах с передачей информации между триггерами возможна только при условии, что перевод триггера в новое состояние осуществляется после завершения передачи информации о прежнем его состоянии в следующий за ним триггер или иное цифровое устройство. Это достигается раздельной подачей синхросигналов на соответствующие триггеры.

Техническим решением, обеспечивающим сокращение числа тактовых импульсов в цепях управления цифровыми устройствами является применение двухступенчатых триггеров, позволяющих в одном и том же такте производить съем информации и запись новой. Т. е. двухступенчатый триггер состоит из двух одноступенчатых. В начале информация записывается в первый (управляющий) триггер, а затем переписывается во второй (управляемый или ведомый). Такой принцип построения триггеров иногда называют MS-принципом (от англ. master-slave, что буквально означает хозяин-раб), а сам триггер такой триггер называют MS-триггером. В качестве иллюстрации на рис. 3.27 приведена схема двухступенчатого R-S-триггера и его условное обозначение.

Схема двухступенчатого R-S-триггера (а) и его условное обозначение (б)

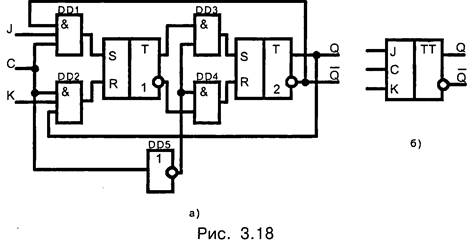

На рис. 3.28 приведена схема наиболее распространенного двухступенчатого J-K-триггера.

Схема двухступенчатого J-K-триггера (а) и его условное обозначение (б)

Синтез двухступенчатых триггеров.

Как следует из закона функционирования двухступенчатых триггеров, их синтез определяется синтезом соответствующего одноступенчатого триггера в заданном элементном базисе, синтезом управляемого триггера, представляющего собой как правило обычный асинхронный триггер, и синтезом схемы связи. В общем виде алгоритм синтеза двухступенчатого триггера может быть представлен в реализации следующих пунктов:

1. Для определенной элементной базы синтезируется соответствующий триггер (управляющий);

2. В заданном элементном базисе синтезируется управляемый триггер. (Обычно управляемый и управляющий триггеры синтезируются в одном и том же элементном базисе);

3. Через элементы связи (схему связи) осуществляется коммутация выходов управляющего триггера со входами управляемого триггера.

В соответствии с алгоритмом синтеза получаем следующую схему:

Схема двухступенчатого D-триггера (а) и его условное обозначение (б)

Универсальные триггеры

Триггеры, которые могут работать в различных режимах, называются универсальными. Наиболее популярны как универсальные триггеры это D-триггеры и J-K-триггеры. Пусть, например, имеем следующее включение D-триггера:

|

Как известно, характеристическое уравнение D-триггера имеет вид:

Для данной схемы имеем:

Для J-K-триггера наиболее широко применяются схемы включения:

|

1. Счетный режим. Действительно: т.к. характеристическое уравнение J-K-триггера имеет вид:

|

2. D-триггер. Приняв

3. R-S-триггер. Согласно определению J-K-триггера (точнее закону его функционирования) J-K-триггер может работать и как R-S-триггер, причем как асинхронный (по установочным входам) и как синхронный.

Наряду с триггерами, тактируемыми импульсами (потенциальное управление) широко применяются триггеры с динамическим управлением, тактируемые фронтом синхроимпульса, и которые используют специальную схемотехнику. Прием информации происходит в момент смены уровней сигнала на синхронизирующем входе. Но это уже другая тема.

Литература.

Двухступенчатые триггеры

Т-триггер, или, как его часто называют, счетный триггер, согласно определению входов, должен изменять свое состояние на противоположное по каждому активному логическому сигналу, действующему на информационном входе T. Данному алгоритму работы соответствует таблица переходов (табл. 5), в которой активным считается сигнал лог. 1, и логическое выражение вида

Это выражение характеризует работу асинхронного T-триггера. Используя (5) и замечания, сделанные при рассмотрении синхронного RS-триггера, можно легко получить выражение для синхронного T-триггера:

Реализация данного режима работы с использование простейшего элемента памяти требует подачи на последний для каждого последующего переключения инверсных значений входных сигналов. Такой режим обеспечивается введением в RS- или D-триггер цепей дополнительной обратной связи (рис. 5).

Рис. 5. Асинхронные Т-триггеры на основе RS- (а) и D-триггеров (б)

Полученные структуры соответствуют алгоритму работы Т-триггера. Однако на практике они не могут обеспечить его надежное функционирование. Это связано с тем, что элемент памяти в данном случае одновременно должен быть источником и приемником информации. Очевидно, что одновременное выполнение этих функций одним триггером невозможно, так как прием новой информации автоматически означает потерю старой. Поэтому при идеальном быстродействии используемых логических элементов приведенные структуры неработоспособны. Также они неработоспособны и при использовании элементов, обладающих собственной инерционностью, либо внешних цепей задержки (рис. 5). Объясняется это следующим: если к моменту изменения сигналов на входах R, S или D сигнал T еще не снят, происходит следующее переключение триггера (он начинает функционировать как генератор незатухающих колебаний). Для их устранения необходимо использовать дополнительный элемент памяти, запоминающий новые значения сигналов R, S или D и подающий их на информационные входы основного элемента памяти только после снятия активного сигнала со входа T, либо искусственно ограничивать длительность сигнала T. Эти принципы реализованы в двухступенчатых триггерах и триггерах с динамическим управлением.

В двухступенчатом триггере противоречия между процессами хранения старой и приемом новой информации решены введением второго запоминающего элемента. Новая информация формируется сначала только во входной ступени триггера при сохранении старой информации в выходной его ступени. Когда новое состояние входной ступени сформировано и снят активный уровень сигнала со входа Т, происходит ее перезапись в выходную ступень устройства. Таким образом, двухступенчатый триггер фактически состоит из двух последовательно соединенных триггеров – ведущего и ведомого (рис. 6).

Рис. 6. Двухступенчатый Т-триггер

Для устранения режима автоколебаний синхронизация работы ведущего и ведомого триггеров осуществляется инверсными логическими уровнями. Часто двухступенчатый триггер называют MS-триггером. По структуре двухступенчатого могут быть построены любые типы триггеров.

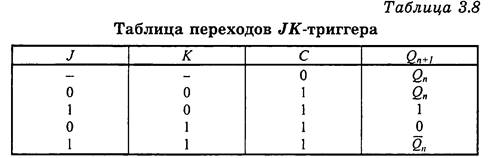

JK-триггер является наиболее универсальным триггером, так как на его основе могут быть выполнены любые из описанных ранее типов триггеров. В отличие от RS-триггера, JK-триггер не имеет запрещенных комбинаций входных сигналов и его таблица переходов (табл. 6) в предположении, что активным является сигнал лог. 1, имеет вид:

Эта таблица отражает определение входов J и K, которые при подаче на них активного входного сигнала соответственно устанавливают и сбрасывают JK-триггер.

ФАЛ, описывающие работу асинхронного и синхронного JK-триггеров:

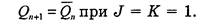

Из таблицы переходов JK-триггера видно, что при подаче на информационные входы J и K сразу двух активных логических уровней, триггер работает как счетный. Следовательно, структурная схема данного триггера должна повторять схему Т-триггера, т.е. должна содержать дополнительные цепи обратной связи. Поэтому структура JK-триггера базируется на структуре MS-триггера или триггера с динамическим входом (рис. 7).

Рис. 7. Структурная схема JK-триггера

Поскольку введение обратных связей решает задачу исключения запрещенных комбинаций входных сигналов, входы J и K могут функционировать как входы R и S RS-триггера.

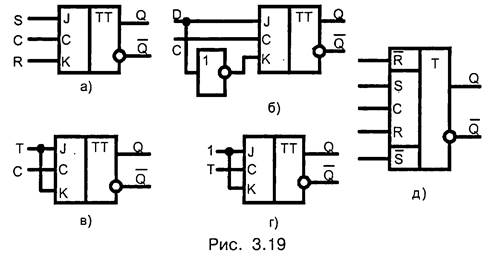

Рис. 8. Построение триггеров на основе JK-триггера:

а – синхронный RS-триггер; б – D-триггер; в – синхронный Т-триггер;

г – асинхронный RS-триггер; д – асинхронный Т-триггер

Двухступенчатые триггеры

Рис. 4.4; Двухступенчатый RS-триггер

Управляющие S- и R-сигналы могут обновляться по спаду того же синхроимпульса, который управляет триггером, и триггер при этом всегда будет воспринимать лишь предыдущее, еще не обновленное состояние S и R сигналов. На этом свойстве держится вся идеология однофазной синхронизации.

Свойство непрозрачности MS-триггера использовано для построения широко применяемого JK-триггера, схема которого показана на рис.4.5,а

JK-триггер-это непрозрачный триггер, выходы которого петлями обратных связей накрест заведены на входные конъюнкторы 1 и 2. Внешние входы самого триггера при этом принято называть уже не S и R, а J и К.

При J= K=0 С-сигнал не может открыть входные элементы 1 и 2, и триггер находится в режиме хранения. При J=1, К=0 синхросигналом может быть открыт лишь элемент 1 и только при условии, что перед поступлением С-сигнала на выходе триггера был 0 (Q=0). Тогда по спаду синхросигнала триггер переключится в «1». Если же триггер до синхросигнала был в «1», то он так и останется в «1». Таким образом, J-вход выполняет функции синхронизированного S-входа. В силу симметрии схемы легко показать, что K-вход выполняет функции синхронизированного R-входа, переводя триггер в «0». Таким образом, при разных уровнях на J- и К-входах JK-триггер ведет себя как синхронный непрозрачный RS-триггер.

Существенно отличным от RS-триггера является поведение JK-триггера при J=K=1. Для RS-триггера такое сотояние входов запрещено. Диаграмма работы JK-триггера в этом режиме показана на рис. 4.5,б. При любом состоянии триггера сигналы обратной связи открывают для С-сигнала именно тот входной конъюнктор, пройдя через который, С-сигнал переведет триггер в противоположное состояние. Таким образом, при J=K=1 по спаду каждого С-сигнала JK-триггер меняет состояние своих выходов на противоположное. Это так называемый счетный режим, или Т-режим работы триггера (от toggle—кувыркаться).

Кратко функционирование JK-триггера описывается табл. 4.1. Новым символом в таблице является символ спада синхроимпульса, который изображается направленной вниз стрелкой. Таблица отражает тот факт, что для JK-триггера переключающей сущностью синхроимпульса является не уровень его, а перепад уровня.

| Режим | С | Jt | Kt | Qt+1 |

| Хранение | X |  | ||

| Сброс | ¯ | |||

| Установка | ¯ | |||

| Инверсия предыдущего состояния | ¯ |  |

|

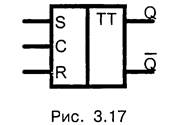

Схема, близкая к показанной на рис. 4.5, а, лежит в основе триггера К155ТВ1. Эта микросхема имеет тройные конъюнктивные входы J и K, т.е. сам двухступенчатый триггер получает J или K сигнал лишь при совпадении единиц на всех трех J или K входах микросхемы. Условное обозначение двухступенчатого JK триггера, имеющего тройные входы, показано на рис. 4.5, в. Две буквы Т указывают на наличие двух ступеней. Вход С, реагирующий не на уровень потенциала С, а на его отрицательный перепад, выделен специальным значком. Вход, реагирующий именно на перепад, иногда называют динамическим.

Дата добавления: 2016-01-18 ; просмотров: 1364 ; ЗАКАЗАТЬ НАПИСАНИЕ РАБОТЫ

Двухступенчатые триггеры

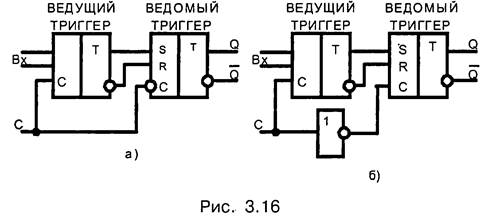

Триггеры с двухступенчатым запоминанием информации состоят из двух триггерных структур. Одна называется ведущий триггер, другая — ведомый триггер (рис. 3.16)

Оба триггера — синхронные, но имеют противоположные синхровходы. На рис. 3.16 ведущий триггер срабатывает при С = 1, имеет прямой синхронизирующий вход, а ведомый при С = 0 — инверсный синхронизирующий вход.

На первом этапе, когда происходит запись информации в ведущий триггер, ведомый отключен, продолжает сохранять предыдущее состояние. Когда снят активный уровень с синхровхода ведущего триггера, происходит перезапись информации в ведомый триггер. Таким образом, происходит поэтапная запись информации благодаря управлению инверсными логическими уровнями.

В двухступенчатом триггере устраняется противоречие между процессами хранения старой и приема новой информации. Это дает возможность построения синхронных автоматов без опасных временных состояний, исключить предпосылки к режиму генерации. Позволяет обеспечить высокую надежность функционирования триггеров с внутренними цепями обратной связи. В то же время схемы этих триггеров более сложные, чем схемы триггеров с динамическим входом, а быстродействие ниже.

JK-триггер

JK-триггеры — это двухступенчатые универсальные синхронные триггеры. Универсальность заключается в том, что на их основе можно сделать любой другой тип логических триггеров RS, D, Т. Вход J аналогичен входу S уже рассмотренного RS- триггера, т.е. устанавливает в единичное состояние Q=1 при J=1.Вход К устанавливает JK-триггер в нулевое состояние, т. е. аналогичен входу R: Q = 0 при К = 1.

Отличие от RS-триггера заключается в том, что JK- триггер не имеет запрещенных входных комбинаций. Если на оба входа J и К подать активный логический уровень, то триггер перейдет в состояние, противоположное предыдущему: Qn+1= 0, при J = К = 1.

Входной сигнал зависит не только от состояния входных сигналов, но и от предыдущего состояния JK-триггера.

На основе JK-триггера может быть построен любой другой триггер (рис. 3.19). На рис. 3.19, а — синхронный RS-триггер, на рис. 3.19, б — D-триггер, на рис. 3.19, в — синхронный Т-триггер, на рис. 3.19, г — асинхронный Т-триггер.

JK-триггер, как и другие типы триггеров, может дополнительно иметь входы начальной установки (рис. 3.19, д), которые являются инверсными по отношению ко входам J, К.

JK-триггеры — это более сложные триггеры, содержат большее число элементов, поэтому потребляемая мощность Рпот оказывается большой. Меры, принимаемые к уменьшению потребляемой мощности, нередко приводят к ухудшению частотных свойств. JK-триггер вследствие своей универсальности и отсутствия запрещенных комбинаций находит широкое применение в цифровой технике.

Счетчики

Счетчиком называется последовательностное устройство, предназначенное для счета входных импульсов и фиксации их числа. Счет импульсов является одной из наиболее распространенных операций в устройствах дискретной обработки информации.

Основное функциональное назначение счетчиков:

1. счет импульсов, поступивших на вход;

Из определения и логики работы счетчиков следует, что их текущее состояние зависит не только от нового пришедшего импульса, но также и от количества предыдущих импульсов. Значит, счетчики относятся к устройствам с памятью. Строятся счетчики на основе однотипных связанных между собой триггеров. Наиболее часто используются Т- и JK-триггеры. Ведь T-триггеры так и называются — счетные триггеры. С другой стороны в JK-триггерах обеспечивается смена состояния на противоположное предыдущему

Комбинационные элементы в счетчиках используются для управления работой триггеров. Число триггеров определяет максимальное количество импульсов, которое может быть подсчитано счетчиком.

В счетчиках выполняются следующие логические операции:

1. установка в нулевое состояние (сброс);

2. запись входной информации в параллельной форме — начального кода, с которого начинается счет;

3. хранение записанной информации;

4. выдача хранимой информации в параллельной форме;

5. инкремент — увеличение хранящегося числа на единицу;

6. декремент — уменьшение хранящегося числа на единицу.

Основным параметром счетчика является модуль счета М, равный максимальному числу импульсов, после которых счетчик устанавливается в исходное состояние (обнуляется) и начинается новый цикл работы счетчика.

По значению модуля счета различают:

· двоично-кодированные, в которых модуль счета может быть любом числом, не равным 2.

По направлению счета счетчики бывают:

· суммирующие (прямого счета), в которых происходит увеличение состояния счетчика — инкремент;

· вычитающие (обратного счета), в которых состояние счетчика уменьшается — декремент;

· реверсивные, которые по управляющему сигналу могут как увеличивать, так и уменьшать свое состояние.

Как и все цифровые устройства, счетчики бывают синхронные и асинхронные.

Быстродействие счетчиков характеризуется временем установления в нем нового состояния, а также максимальной частотой следования поступающих импульсов.

Отечественные микросхемы счетчики можно определить по маркировке функционального назначения буквами ИЕ, например, К555ИЕ2. На принципиальных схемах счетчики обозначаются буквами СТ2, СТ10.

По способу кодирования внутренних состояний различают двоичные счетчики, счетчики Джонсона, счетчики с кодом «1 из N», счетчики в коде Грея и др. Наибольшее распространение получили двоичные счетчики, а из двоично-кодированных чаще всего применяют двоично-десятичные. Счетчики с другим модулем счета можно получить путем введения дополнительных связей между разрядами.

Двоичные счетчики

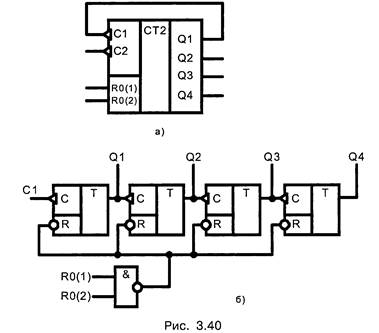

Работу асинхронного счетчика рассмотрим на примере микросхемы К555ИЕ5 — четырехразрядного двоичного счетчика на двухступенчатых счетных триггерах. Этот счетчик имеет два счетных входа С1,С2 и два входа установки нуля R0 (1), R0 (2) (рис. 3.40).

Триггеры срабатывают по срезу входного импульса (при переходе из 1 в 0). Четыре последовательно соединенных триггера образуют счетчик модулю 2 4 = 16. Максимально хранимое в счетчике число полном его заполнении

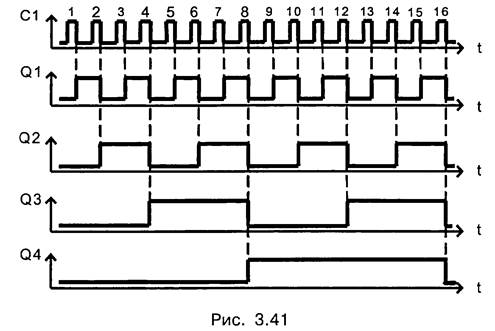

Из таблицы 3.16 и рис. 3.41 видно, что при срабатывании по заднему фронту (срезу) триггеры имеют инверсные динамические входы. Состояние счетчика в двоичном коде по приходу на вход каждого нового импульса увеличивается на единицу, осуществляется операция инкремента.

Так как счетный триггер делит частоту входных импульсов на два, то цепочка из четырех последовательно соединенных триггеров делит частоту на 16. По приходу каждого шестнадцатого импульса счетчик обнуляется и цикл счета начинается сначала.

Представленный на рис. 3.40 счетчик является суммирующим.

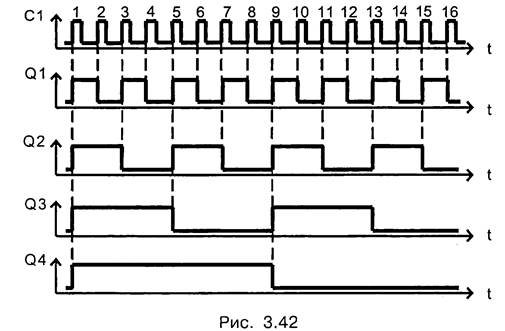

Если исходные асинхронные Т-триггеры имеют прямые динамические входы, срабатывают по переднему фронту импульса при переходе из 0 в 1, то счетчик превращается в вычитающий. Он выполняет операцию декремента. Временные диаграммы такого счетчика приведены на рис. 3.42.

В обоих рассмотренных случаях для синхронизации каждого последующего асинхронного T-триггера использовался прямой выход предыдущего триггера Q. Если ко входам подключать инверсный выход Q, то суммирующим будет счетчик с прямыми динамическими входами.

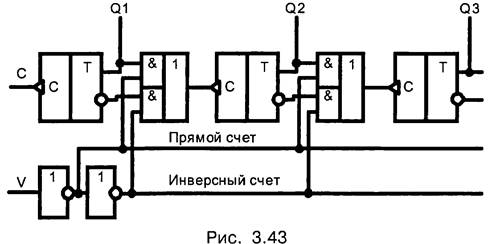

Используя различные варианты прямого и обратного счета, можно получить реверсивный счетчик. Такое переключение осуществляется с использованием элементов И- ИЛИ, И-ИЛИ-НЕ, которые устанавливаются между триггерами (рис. 3.43).

При поступлении на вход V логического нуля V = 0 на выходы верхних по схеме элементов И поступает логическая единица и к инверсным динамическим входам триггеров подключены прямые входы предыдущих триггеров. Счетчик выполняет операцию суммирования. При подаче сигнала V = 1 по входам триггеров (инверсным динамическим) подключается инверсный выход предыдущих триггеров и выполняется операция вычитания.

На рис. 3.43 показан один из вариантов построения реверсивного счетчика. Возможны и другие варианты, использующие тот же самый принцип организации межразрядных связей.

В рассмотренных счетчиках при последовательном соединении триггеров переключение каждого триггера может произойти только после переключения предыдущего. Поэтому они называются счетчиками с последовательным переносом. Такие счетчики отличаются простой схемой, но в то же время имеют наибольшее время установления выходного кода, которое к тому же является различным при различном состоянии счетчика. Например, если в счетчике записаны числа 010 = 00002, 01002= 410, и т. д., то переключается только один триггер, а при переходе из состояния 1510= 11112, либо 710 = 01112 переключаются все четыре триггера. Новый тактовый импульс можно подавать на счетчик после того, когда установятся все триггеры. Таким образом, период следования Т входных импульсов должен удовлетворять соотношению

где N — число разрядов счетчика;

Уменьшить время установления можно при условии, что все разряды счетчика будут переключаться одновременно. В этом cлучае следует отказаться от асинхронных счетчиков и перейти к использованию синхронных.

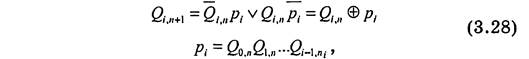

Из анализа таблицы 3.16 и рис. 3.41 для суммирующего асинхронного счетчика отметим: переключение каждого i-ro триггера происходит по приходу нового входного импульса при условии, что все предыдущие триггеры находятся в единичном состоянии. В этом случае i—й триггер меняет свое состояние. Математически с помощью формул алгебры логики данный алгоритм записывается

где pt — сигнал переноса;

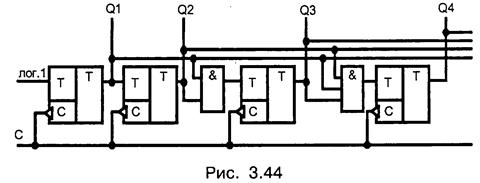

Из формул 3.28 следует, что сигнал переноса pi формируется с помощью многовходовых элементов И. На рис. 3.44 представлен фрагмент схемы.

В схеме на рис. 3.44 все триггеры устанавливаются одновременно по приходу синхроимпульса С. Время установки счетчика равно времени задержки в одном разряде. Счетчики, реализующие алгоритм (3.28), называются счетчиками с параллельным переносом. Они имеют значительно более высокое быстродействие.

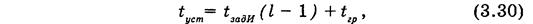

Повышение быстродействия достигается за счет усложнения схемы. Время установления tycm таких счетчиков не зависит от числа разрядов и равно

Однако, с ростом числа разрядов реализация параллельных счетчиков вызывает затруднения. Растет число входов элементов И, растет нагрузка на выходы триггеров. Кроме того, одновременное переключение сразу многих триггеров в счетчике создает значительный импульс тока в цепях питания.

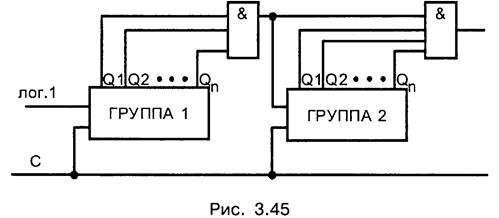

Поэтому при большом числе разрядов используют комбинированную структуру последовательно — параллельного переноса. Суть данной организации состоит в объединении нескольких триггеров в группы. Формирование сигнала переноса осуществляют между группами (рис. 3.45)

Сигнал переноса из группы триггеров возникает при условии, что все триггеры этой группы находятся в единичном состоянии.

Упрощение комбинированного счетчика с последовательно- параллельным переносом приводит к некоторому снижению его быстродействия:

где l — число групп;

t — время задержки (установления) в группе.

При необходимости формирования счетчиков большой размерности и уменьшения импульсов тока при переключении переходят к формированию счетчиков в коде Грея. Суть кода Грея заключается в том, что при переходе от одной кодовой комбинации к следующей соседней изменяется состояние только одного разряда. Однако полученный результат затем необходимо перевести в двоичный код с использованием преобразователя кода.

Дата добавления: 2015-11-20 ; просмотров: 10053 ; ЗАКАЗАТЬ НАПИСАНИЕ РАБОТЫ